Implement Software-Defined Radio for IoT with Custom FPGA Boards

The Internet of Things (IoT) encompasses such a broad array of applications that often a single design requires more than one wireless interface, adding space, power, and cost. An alternative path to the flexibility needed to support multiple, constantly evolving standards for savvy IoT network designers is to use software-defined radio (SDR) technology.

The idea of SDR isn't new; what’s new is how SDR has been adapted to solve the IoT dilemma of incorporating multiple RF technologies on the same network infrastructure while simplifying designs, shortening development cycles, and reducing overall cost.

This article presents an SDR design based on a custom FPGA board that was used to create a multi-protocol wireless digital baseband solution.

SDR Adds Performance and Efficiency for Network Sockets

As the name implies, SDR technology can support multiple radio protocols on the same hardware. Depending on the implementation, it can support those protocols simultaneously and across a broad (or narrow) swath of spectrum. And when implemented using FPGAs in a wireless device like a base station, SDR platforms can even be reprogrammed to future-proof network infrastructure as wireless connectivity protocols continue to evolve.

A good example of the potential of SDR is VotaryTech’s SDR platform, the Arria 10AX115U3F4512SG (Figure 1). This Intel® Arria® 10 FPGA SoC-enabled networking card can serve a broad range of wireless applications, including Global System for Mobile Communications (GSM), General Packet Radio Service (GPRS), wideband signal processing for LTE networks, tracking, and telemetry. The board is a front-end RF platform that supports wireless applications ranging from 70 MHz to 6 GHz, though it is expandable to frequencies up to 15 GHz.

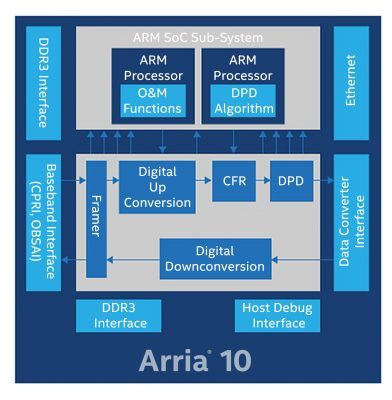

The custom 10AX115U3F4512SG supports all signal-processing requirements of networking applications, including various modulation and demodulation schemes. The board's baseband processing capabilities encompass digital up-conversion, digital down-conversion, and standard modulator and demodulator communication cores. This allows this SDR platform to support both transmit and receive signals in a wireless design.

Furthermore, the 10AX115U3F4512SG enables programmable and fine-tunable baseband processing inside the Arria 10 FPGA, where tasks such as IF filtering and down-conversion can be performed.

Why Use an FPGA in SDR

Early SDR designs built around RF front-end modules fascinated engineers and showed great potential. But as a technology in search of applications, SDR designs didn't really make tangible progress. This was due in part to the requirement (and cost) of custom ASICs in such systems.

But today, low-risk SoCs are replacing the traditional ASICs used in SDR platforms. For example, mid-range FPGA SoCs like the Intel Arria 10 built on 20-nm process technology deliver up to 15 percent higher performance and consume 60 percent less energy compared to prior-generation high-end FPGAs (Figure 2). The devices also generate significantly less heat, a vital consideration in wireless base station, mobile backhaul, and remote radio head designs.

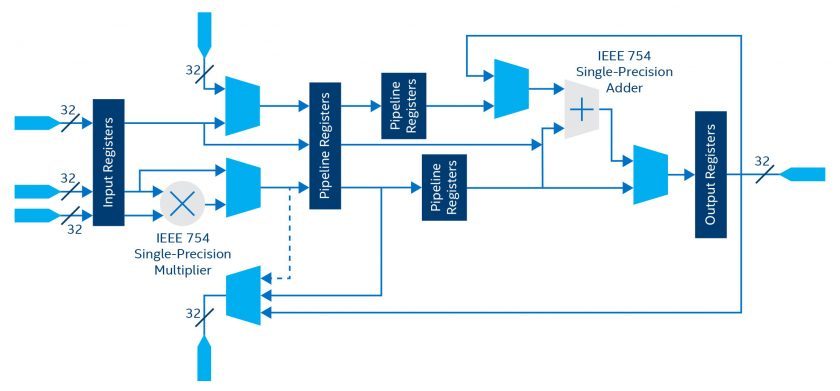

More important, Intel Arria FPGA SoCs offer a number of variable-precision DSP blocks and dual-core Arm Cortex-A9 processor options. The DSP blocks in the Arria 10 FPGA SoC are available in three modes: standard-precision fixed-point, high-precision fixed-point, and single-precision floating-point (Figure 2). These allow wireless system designers to implement a variety of algorithms for digital up- and down-conversion and multi-rate filtering.

Combine these compute capabilities with more than 1 million FPGA logic elements (LEs) and a 2,400 Mbps DDR4 SDRAM memory interface, and the result is a highly programmable, adaptable platform that can accommodate current and emerging wireless technologies (Figure 3).

Synthesizable IP cores can also be integrated into the FPGA fabric that allows wireless equipment designers to provide both analog-to-digital converter (ADC) outputs and digital-to-analog converter (DAC) inputs to the baseband inside the FPGA. That, along with I/O and protocol control, plays a critical role in facilitating the SDR-based RF processing and baseband interface.

Easy access to circuit schematics and the availability of Gerber and board files for the 10AX115U3F4512SG simplify integrating SDR functionality. The Arria 10's support for the Common Public Radio Interface (CPRI) specification also boosts the platform's suitability to wireless base station design.

Programmability Reaches IoT Doorstep

VotaryTech originally developed this SDR design for a wireless modem application, but since the hardware is programmable it can also be used in applications such as telemetry and waveform generation simulators. This flexibility, enabled by Arria 10 FPGA SoCs, also makes boards like the 10AX115U3F4512SG well suited to IoT deployments like the IoT that consist of a wide array of evolving technologies and applications.

But perhaps most important, this article has demonstrated how smaller design houses can exploit the power of highly configurable FPGA SoC devices to deliver solutions that accommodate both current and future requirements.